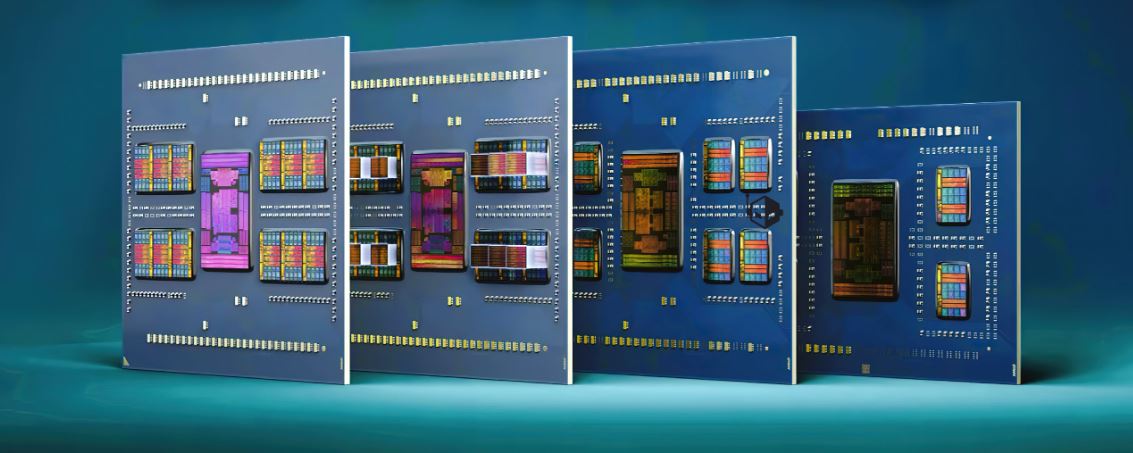

AMD will introduce the Epyc 9005 processors (Turin) in autumn 2024. With 128 Zen 5 cores, these processors will not only have the highest number of performance cores but also the highest cache density to date without using 3D V-Cache. The layout of the CCDs (Core Complex Die) has most likely been adjusted to achieve this. However, AMD has not yet revealed any details.

Please follow us on Twitter and Facebook

To accommodate 128 Zen 5 cores, each chiplet contains 16 cores, compared to the previous maximum of eight active cores per CCD. The cores will continue to be divided into two clusters (CCX), similar to the Bergamo processors (Epyc 9004) with Zen 4c cores, where AMD first installed 16 cores per CCD. This was made possible due to the reduced area required by the Zen 4c cores

AMD is also planning a high-density successor for Zen 5, code-named Prometheus. In this version, AMD will install twelve CCDs with 16 cores each, so the top model should have 192 cores and 384 threads. This is achievable due to the 25 percent reduction in the area required by the Zen 5c cores, although this reduction comes at the expense of the maximum possible clock frequency.

Read Also: AMD Ryzen 9000 ‘Strix Halo’ Notebook Chips Leak with Zen 5 CPU and High AI Performance

Even More Cache Through 3D Stacking

It is well-known that Zen 5 will also be released in a version with 3D V-Cache. In the desktop sector, the X3D processors are expected as early as autumn 2024. For servers, AMD is likely to wait a little longer before announcing Turin-X.

| Series | Model | Cores/Threads | Architecture | L3 Cache |

| Prometheus | Epyc9855* | 192 / 384 | Zen5c | 384 MB* |

| Turin-X | Epyc9755X* | 128 / 256 | Zen5 | 1,536 MB* |

| Torino | Epyc9755* | 128 / 256 | Zen5 | 512 MB |

| Bergamo | Epyc9754 | 128 / 256 | Zen4c | 256 MB |

| Genoa | Epyc9654 | 96 / 192 | Zen4 | 384 MB |

| Genoa-X | Epyc9684X | 96 / 192 | Zen4 | 1,152 MB |

AMD Epyc 9005 (Turin) – *Not officially announced

The amount of additional cache AMD will install is still unknown. By switching to CCDs with twice as many processing cores, the cache would need to be increased accordingly to reach 1.5 GB. Unless AMD considers an additional 64 MB per CCD to be sufficient, then an AMD Epyc-9785X (Turin-X) would have 1,024 MB of L3 cache, less than the current Epyc-9754X with 96 cores and 1,152 MB of L3 cache.